- 您现在的位置:买卖IC网 > Sheet目录1905 > ATMEGA644P-B15MZ (Atmel)IC MCU 8BIT 64KB FLASH 32VQFN

50

7674F–AVR–09/09

ATmega164P/324P/644P

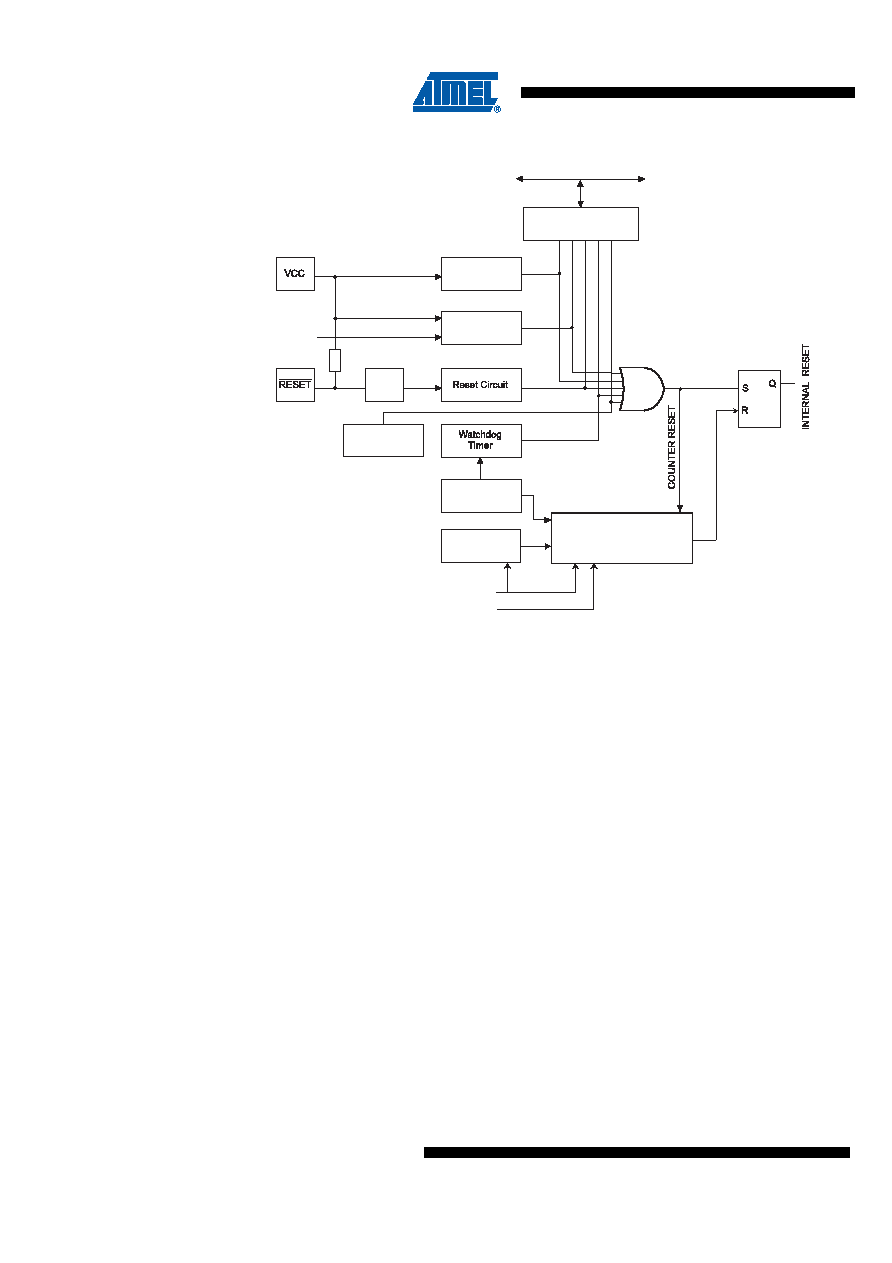

Figure 9-1.

Reset Logic

9.0.3

Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The detection level

is defined in “System and Reset Characteristics” on page 332. The POR is activated whenever

V

CC is below the detection level. The POR circuit can be used to trigger the start-up Reset, as

well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the

Power-on Reset threshold voltage invokes the delay counter, which determines how long the

device is kept in RESET after V

CC rise. The RESET signal is activated again, without any delay,

when V

CC decreases below the detection level.

MCU Status

Register (MCUSR)

Brown-out

Reset Circuit

BODLEVEL [2..0]

Delay Counters

CKSEL[3:0]

CK

TIMEOUT

WDRF

BORF

EXTRF

PORF

DATA BUS

Clock

Generator

SPIKE

FILTER

Pull-up Resistor

JTRF

JTAG Reset

Register

Watchdog

Oscillator

SUT[1:0]

Power-on Reset

Circuit

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATMEGA644V-10PU

IC AVR MCU FLASH 64K 40DIP

ATMEGA645V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA649-16MI

IC AVR MCU FLASH 64K 5V 64QFN

ATMEGA649V-8MI

IC AVR MCU FLASH 64K 1.8V 64QFN

ATMEGA8515L-8JUR

MCU AVR 8KB FLASH 8MHZ 44PLCC

ATMEGA8515L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

ATMEGA8535-16JUR

MCU AVR 8K FLASH 16MHZ 44PLCC

ATMEGA8535L-8PJ

IC MCU AVR 8K 5V 8MHZ 40-DIP

相关代理商/技术参数

ATMEGA644PR212-AU

功能描述:8位微控制器 -MCU ATmega 644PV-10AU AT86RF212-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR212-MU

功能描述:8位微控制器 -MCU ATmega 644PV-10MU AT86RF212-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR231-AU

功能描述:8位微控制器 -MCU ATmega 644PV-10AU AT86RF231-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PR231-MU

功能描述:8位微控制器 -MCU ATmega 644PV-10MU AT86RF231-ZU RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AQ

功能描述:8位微控制器 -MCU AVR 64KB, 2KB EE 20MHz 4KB SRAM, 1.8V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AQR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM-20MHz, 5V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AU

功能描述:8位微控制器 -MCU AVR 64K FLASH 2K EE 4K SRAM ADC-10MHZ RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

ATMEGA644PV-10AUR

功能描述:8位微控制器 -MCU AVR 64KB FLSH 2KB EE 4KB SRAM-10MHz, 1.8V RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT